Verilog Code For Serial Adder Subtractor Using Ripple

Design and simulate an 8-bit adder/subtractor using a hierarchical Verilog structural description. Your design should accept 2 twos complement 8-bit inputs (x and y) and generate an output (result) which is either their sum or difference, based on another input (sub). If sub is 1, perform a subtract; if sub is 0 perform an addition. 2d fighter maker 2002 v1 o2 fitness.

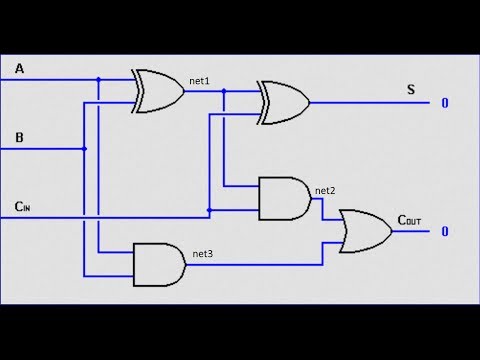

Adder and Subtractor Circuits Objective: (i) To construct half and full adder circuit and verify its working. Are called a ripple-carry adder, since the carry bit “ripples” from one stage to the next. Persamaan transistor d8050. The schematics for a 4-bit full adder circuit is shown. Modified SQRT CSLA architecture using zero finding logic. I have internal diagram nd it is prposed Square root Carry Select Adder 16 bit using zero finding logic for ripple carry adder for input Carry =1 and multiplexer to optimize the area and power.

You must also set four condition bits (ccn, ccz, ccv, ccc) to indicate whether the result is negative, zero, resulted in an overflow, resulted in a carry out, respectively. Create the design in a hierarchical fashion as follows. Build a 1-bit full adder using a behavioral dataflow description.

Create a testbench to thoroughly test the full adder. Then, create an 8-bit ripple carry adder by instantiating and connecting multiple instances of your debugged full adder. Write a testbench to verify your 8-bit ripple carry adder. Do not use any delay in your design modules. You must declare your 8-bit adder/subtractor exactly as follows: module AddSub8Bit (x, y, sub, result, ccn, ccz, ccv, ccc); input [7:0] x, y; input sub; output [7:0] result; output ccn, ccz, ccv, ccc; Below are my 1bitadder, 8bitfulladder, I need help on the last part 8-bit adder/subtractor and making my design that it takes 2 twos complement 8-bit inputs (x and y) and generate an output (result) which is either their sum or difference, based on another input (sub) plus (ccn, ccz, ccv, ccc).

Please help me.